# A GPU-parallelization of the neXtSIM-DG dynamical core (v0.3.1)

Robert Jendersie<sup>1,2</sup>, Christian Lessig<sup>1,3</sup>, and Thomas Richter<sup>2</sup>

**Correspondence:** Robert Jendersie (robert.jendersie@ovgu.de)

Abstract. The cryosphere plays a crucial role in Earth's climate system, making accurate sea ice simulation essential for improving climate projections. To achieve higher resolution simulations, graphics processing units (GPUs) have become increasingly appealing due to their higher floating point peak performance and superior energy efficiency compared to CPUs. However, harnessing the full theoretical performance of GPUs often requires significant effort in redesigning algorithms and careful implementation. Recently, several frameworks have emerged, aiming to simplify general-purpose GPU programming. In this study, we evaluate multiple such frameworks, including CUDA, SYCL, Kokkos, and PyTorch, for the parallelization of neXtSIM-DG, a finite-element-based dynamical core for sea ice. Based on our assessment of usability and performance, CUDA demonstrates the best performance, while Kokkos is a suitable option for its robust heterogeneous computing capabilities. Our complete implementation of the momentum equation using Kokkos achieves a sixfold speedup on the GPU compared to our OpenMP-based CPU code, while maintaining competitiveness when run on the CPU. Additionally, we explore the impact of different discretization orders and the use of lower precision floating-point types on the GPU, showing that switching to single precision can further accelerate sea ice codes.

# 1 Introduction

Simulations are essential for understanding the effects of climate change and enabling stakeholders to mitigate its impact on societies and individuals (Jakob et al., 2023). The cyrosphere is a key component of Earth's climate system and it has a particular impact on long-term processes. neXtSIM-DG is a novel sea ice code that is designed as part of The Scale-Aware Sea Ice Project (SASIP)<sup>1</sup> to improve both the representation of physical processes and the efficiency and accuracy of numerical implementation.

A crucial factor for the fidelity and reliability of climate simulations is horizontal resolution, with kilometer-scale, convection-resolving simulations being the target for the next generation of models (Stevens et al., 2019; Bauer et al., 2021b). These computations require exascale HPC systems with substantial GPU-based accelerators (Schär et al., 2020; Bauer et al., 2021a). As a result, significant efforts have been dedicated to porting components of existing climate models to GPUs (Ikuyajolu et al., 2023; Sauer and Muñoz-Esparza, 2020; Cao et al., 2023; Sun et al., 2023).

<sup>&</sup>lt;sup>1</sup>Institute of Simulation and Graphics, Otto-von-Guericke University, Magdeburg, Germany

<sup>&</sup>lt;sup>2</sup>Institute of Analysis und Numerics, Otto-von-Guericke University, Magdeburg, Germany

<sup>&</sup>lt;sup>3</sup>European Centre for Medium-Range Weather Forecasts, Bonn, Germany

<sup>&</sup>lt;sup>1</sup>https://sasip-climate.github.io

In line with these developments, SASIP aims to substantially increase the numerical accuracy of the sea ice component of coupled climate models by using modern higher order discretizations of the governing equations. Kilometer-scale sea ice simulations are also of substantial theoretical interest, as initial investigations show a marked change in the behavior of the commonly used viscous plastic sea ice model when approaching km-scale resolutions (Bouchat et al., 2022; Hutter et al., 2022). Computationally much more efficient models are needed for detailed investigations of this behavior, its relationship with known statistical and physical principles (Marsan et al., 2004), and the role of possible alternative models (Dansereau et al., 2016; Ólason et al., 2022). Kilometer-scale or even higher resolved sea ice forecasts are also in high demand among sea ice forecast users (e.g. Kauker et al. (2021)), even though it is unclear how current systems should be used at such resolutions (Hunke et al., 2020). The role of small-scale sea ice features, such as ridges and leads, in atmosphere-ocean-ice interactions in weather and climate models can also only be speculated on with current 10 km scale resolution models (Esau, 2007; Marcq and Weiss, 2012; Ólason et al., 2021). Highly efficient kilometer-scale sea ice models, either as-stand-alone sea ice models or as sea ice emponents-or in fully coupled climate models, are needed to address these questions.

The neXtSIM-DG dynamical core currently builds on the established viscous plastic So far, the GPU parallelization of sea ice models has received limited attention. The usage of GPUs for the finite-difference based dynamical core of CICE, the Los Alamos sea ice model (Hibler, 1979) and uses a, has been investigated by Rasmussen et al. (2024).

The neXtSIM-DG dynamical core is a flexible framework to model sea ice using a discretization with a higher order discontinuous/continuous Galerkin method (Richter et al., 2023a). At the The algorithmic structure is such that different rheologies can be used. At the core of the implementation is a module that encapsulates the non-linear stress update locally (on each element). Different rheologies, e.g. viscous plastic (Hibler, 1979) or brittle mechanics (Ólason et al., 2022), can be easily realized with it. The outer code is a pseudo-time stepping iteration that corresponds to the mEVP iteration (Bouillon et al., 2013), which is frequently used to approximate the Hibler model and which is essentially identical in all rheologies we consider. To focus on the GPU implementation, we only discuss the viscous-plastic model with the mEVP solver in this manuscript without loss of generality. At the heart of the numerical implementation is a large number of identical operations to be carried out on each mesh element. GPUs, which are based on a data parallel processing modelare ideally suited for this kind of tasks. The GPU parallelization of a finite-difference solver for sea ice is investigated by Rasmussen et al. (2024). are well suited for these kinds of computations.

40

50

55

Besides performance, other factors are also important for the implementation of the neXtSIM-DG dynamical core: the code must be adaptable to future hardware, a long-term support of the software must be guaranteed and is it should be easy to use. Such considerations are vital for the model's adoption and sustained use. With these aspects in mind, we examine the current landscape of general-purpose GPU programming frameworks and compare prototype implementations for the parallelization of finite-element/finite-volume codes like neXtSIM-DG.

The de facto standard for general-purpose GPU programming is CUDA (NVIDIA, 2023a), a highly popular framework for general-purpose GPU programming, though it only supports NVIDIA hardware. Additionally, it often necessitates a dedicated GPU implementation, requiring significant effort for development and performance tuning. As a result, various alternatives have emerged, offering greater flexibility and usability. A focus on ease of use and minimal effort in port-for porting to GPUs

is found in frameworks like OpenMP and OpenACC. These, however, offer less control and fewer performance optimization options compared to CUDA.

SYCL (The Khronos Group, 2023a) and Kokkos (Trott et al., 2022) are frameworks designed for heterogeneous computing, enabling targeting one to target of different compute hardware. A major challenge with these frameworks is achieving near-optimal performance across diverse hardware platforms, particularly in efficiently leveraging to efficiently leverage GPU-specific features such as shared memory or tensor cores.

Another recent alternative is the use of libraries such as jax (Bradbury et al., 2018) and PyTorch (Paszke et al., 2019), which were primarily developed for machine learning. Their backends are built upon high-performance linear algebra libraries that support various hardware architectures and include compilers that efficiently map computations onto these platforms. Examples of such backends include XLA (xla, 2023), Triton (Tillet et al., 2019), and TensorRT (NVIDIA, 2023b).

65

85

With machine learning being a driving force in the development of new accelerator hardware, significant resources are invested in lower precision floating point support. Since these types offer orders of magnitude higher throughput than double precision, which is commonly used in scientific computing, mixed precision the use of lower precision datatypes is a promising direction for further speedups. Analysis of weather simulations For weather simulations, experiments with a reduced-precision emulator indicates that the precision can be reduced for most variables, in some cases down to half precision, without degrading results (Hatfield et al., 2019; Tintó Prims et al., 2019). For example, the Integrated Forecasting System (IFS) of the European Centre for Medium-Range Weather Forecasts has successfully switched to single precision without requiring major code changes (Lang et al., 2021). Climate simulations with a reduced-precision emulator suggest that single precision can be equally accurate even for long term runs (Paxton et al., 2022; Kimpson et al., 2023; Banderier et al., 2024).

To compare the GPU programming frameworks and to investigate the potential speedup of an optimized GPU implementation, we use the different frameworks to port an important part of the neXtSIM-DG dynamical core to run on the GPU. Our results show that SYCL is still immature, suffering from an unreliable toolchain. Dedicated CUDA remains the best option for speed, while Kokkos provides comparable performance and but greater flexibility. PyTorch is currently not a viable alternative to handwritten C++ code, but the new compiler TorchInductor shows promise. We also find that single precision is a strong option to further accelerate our sea-ice simulation. Based on our evaluation, we use Kokkos to implement the complete momentum equation on GPU, for which we achieve a speedup by a factor of 6 compared to a multi-core CPU implementation.

The structure of the paper is as follows. We start in Section Sect. 2 with an overview of the neXtSIM-DG dynamical core. The different GPU implementations of it are detailed in Sect. 3. In the subsequent Sect. 4, their performance is compared and the impact of mixed precision as well as higher order discretizations is analyzed. In Sect. 5, the Kokkos implementation is extended and practical results are presented. Finally, directions for future work and a summary is provided in Sect. 6.

# 2 Model description

100

For simplicity of the presentation, we restrict ourselves to the viscous—plastic sea ice model introduced by Hibler (Hibler, 1979)

Hibler (1979). For a discussion on of different material laws we refer to the literature (Feltham, 2008). This model Full details on the model and its discretization in neXtSIM-DG are given by Richter et al. (2023a).

The model consists of advection equations for the ice height H and ice concentration A

$$\partial_t H + \operatorname{div}(\mathbf{v}H) = S_H, \qquad \partial_t A + \operatorname{div}(\mathbf{v}A) = S_A,$$

(1)

where the right hand right side terms  $S_H$  and  $S_A$  are describing thermodynamics. In addition, the 2d velocity field  $\mathbf{v}$  is governed by the momentum equation

$$\rho_{\text{ice}} H \partial_t \mathbf{v} = \text{div } \sigma(\mathbf{v}, A, H) + F, \tag{2}$$

where  $\rho_{\text{ice}}$  is the ice density and  $\sigma$  the stress tensor. In F we collect all external forcings that come from wind and ocean current currents. Implicit solvers for the Hibler model suffer from the strong nonlinearities, are costly and call for require advanced numerical solution strategies (Mehlmann and Richter, 2017). Hence, often often explicit iterations in the sense of a pseudo-time stepping is used, namely the mEVP solver (Bouillon et al., 2013). This introduces a subcycling index p and the implicit rheology is approximated by iterating the following system consisting of momentum equation and stress update

$$\boldsymbol{\sigma}^{(p)} = \frac{\alpha}{1+\alpha} \boldsymbol{\sigma}^{(p-1)} + \frac{1}{1+\alpha} \underbrace{\boldsymbol{\sigma}^{(p-1)} + \frac{1}{1+\alpha} \boldsymbol{\sigma}^{(p-1)} + \frac{1}$$

Here, the  $\mathbf{v}_{n-1}$  is the velocity from the previous macro time step. The viscosities  $\eta, \zeta$  depend on velocity  $\mathbf{v}$ , ice height H and ice concentration A, while the ice strength P depends only on H and A. The parameter  $\alpha > 0$  controls parameters  $\alpha, \beta > 0$  control the stability and the speed of convergence. For an infinite number of subcyling steps  $p \to \infty$ , the mEVP iteration converges to the implicit VP limit. In practice, usually 100 to 200 subcyling steps are performed, see Kimmritz et al. (2016) for a discussion.

This approach is also the basis of the neXtSIM-DG implementation. While the advection problems Eq. (1) are solved using a large time step, the momentum equation Eq. (2) and the mEVP iteration Eq. (3) are subcycled with a smaller step size. Often more than 100 substeps are required in each advection step and the main effort lies in the repeated evaluation of the nonlinear material law, see  $\sigma(\mathbf{v}, A, H)$  in Eq. (3). All details on the model and its discretization in neXtSIM-DG are given in Richter et al. (2023a) To use rheologies other than the viscous plastic model, essentially only the local calculation of the stress  $\sigma_{vp}^{(p)}$  needs to be modified.

## 115 2.1 Discretization

120

125

130

135

We briefly sketch the discretization of the model in the neXtSIM-DG dynamical coreand refer to (Richter et al., 2023a) for details. Equations (1) to (3) are discretized on quadrilateral meshes in spherical coordinates. This mesh is topologically fully structured but each consisting of  $N_x \times N_y$  quadrilateral elements. Each element is mapped from a uniform reference element onto the computational element using a bi-linear transformation to allow better alignment with coastlines and a more equal mesh spacing—in the ocean and ice covered regions. Hence, the computational mesh consists of general quadrilaterals in lat/lon coordinates. The curvature is accounted for exactly by weighting all integrals (of the dG formulation) with the functional determinant of the spherical coordinate system. For the advection equations higher order discontinuous Galerkin upwind methods and high order explicit Runge-Kutta schemes are used. The velocity  $\mathbf{v}$  is instead discretized using a continuous Galerkin approach. As the velocity stress coupling has the form of a mixed formulation, a discontinuous Galerkin space is used to represent the stresses. This space must include the gradient of the velocity space for stability.

## 3 Implementation

Starting point for the GPU implementation of neXtSIM-DG dynamical core is the C++ CPU implementation that is described in (Richter et al., 2023a). This OpenMP parallelized CPU code also serves as the baseline for the performance evaluation. The CPU implementation leverages the linear algebra library Eigen (Guennebaud et al., 2010), which is highly optimized and, e.g., exploits CPU vector units. Due to the explicit character of the discretization, and the parametric finite element setup, most computations are matrix-vector or matrix-matrix products with small matrices and vectors, e.g. vectors of size 4. As several vectors and matrices are already available at compile time, e.g. all quantities that refer to the reference element, neXtSIM-DG greatly benefits from Eigen's template-based design. These fixed size matrices do not require dynamic memory allocation and operations involving such matrices can be fully loop-unrolled. Also, the use of expression templates in Eigen eliminates unnecessary temporary variables in expressions involving multiple operations.

Table 1 indicates computational times for the different parts of the dynamical core in a typical sea ice dynamics simulation. The As a numerical test case for all computations, we used the Mehlmann benchmark problem Mehlmann et al. (2021), which has been tested in various sea ice frameworks since its introduction. It models the impact of a cyclone on a dense ice cover and the formation of linear kinematic features. The square domain is of size  $512 \times 512$  km and the simulation typically runs for four days. The mEVP iteration (middle lines of the table from "strain" to "velocity") takes most of the time and the stress update is the single most expensive part. These computations are local on each mesh element and hence scale well with more cores. They are further well suited as computational unit for the evaluation of the different GPU programming frameworks. A pseudocode overview of the stress update computations is shown in Listing 1. The original C++ code is documented in Appendix B. Unless otherwise stated all numerical testcases use double precision. The code ,however, is generic in this respect and Section 4.2 will study the effect of using lower or mixed precision arithmetics.

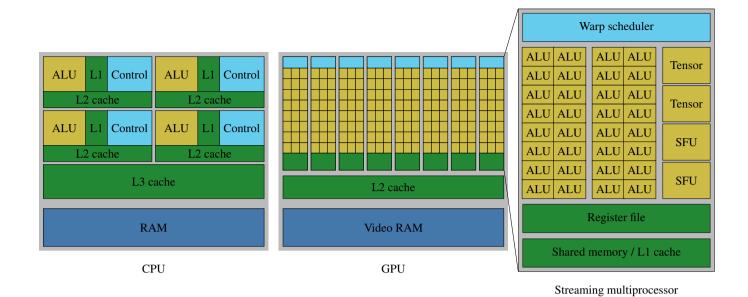

For readers unfamiliar with GPU architecture and the specifics of GPU programming, we provide a brief introduction in Appendix A to complement the following text.

```

1 \DIFaddendFL void StressUpdateHighOrder (Matrix <N, n_S>& S^{11}, Matrix <N, n_S>& S^{12}, Matrix <N, n_S>& S^{22},

const Matrix \langle N, n_S \rangle \& E^{11}. const Matrix \langle N, n_S \rangle \& E^{12}. const Matrix \langle N, n_S \rangle \& E^{22}.

2

const Matrix \langle N, n_A \rangle \& H, const Matrix \langle N, n_A \rangle \& A, double \alpha) {

3

for (i = 0; i < N; ++i) { // in parallel

4

Vector < n_G > h = \max\{0, H_{i,*}PSI\langle n_A \rangle\}

5

Vector < n_G > a = \min\{1, \max\{0, A_{i,*}PSI\langle n_A \rangle\}\}\

6

Vector < n_G > e^{11} = E_{i,*}^{11} PSI \langle n_S \rangle

7

Vector < n_G > e^{12} = E_{i*}^{12} PSI \langle n_S \rangle

8

Vector \langle n_G \rangle e^{22} = E_{i,*}^{22} PSI \langle n_S \rangle

9

10

Vector < n_G > P = P^* \cdot h * exp(-20(1-a))

11

Vector \langle n_G \rangle D = (\Delta_{\min}^2 + \frac{5}{4}(E_{i,*}^{11} * E_{i,*}^{11} + E_{i,*}^{22} * E_{i,*}^{22}) + \frac{3}{2}E_{i,*}^{11} * E_{i,*}^{22} + E_{i,*}^{12} * E_{i,*}^{12})^{\frac{1}{2}}

12

Vector < n_G > P_D = P/D

13

14

S_{i*}^{11} = (1 - \alpha^{-1}) S_{i*}^{11} + \alpha^{-1} M_i^{-1} (P_D * (\frac{5}{8}e^{11} + \frac{3}{8}e^{22}) - \frac{1}{2}P)

15

S_{i,*}^{12} = (1 - \alpha^{-1})S_{i,*}^{12} + \alpha^{-1}M_i^{-1}(P_D * \frac{1}{4}e^{12})

16

S_{i,*}^{22} = (1 - \alpha^{-1}) S_{i,*}^{22} + \alpha^{-1} M_i^{-1} \left( P_D * \left( \frac{5}{9} e^{22} + \frac{3}{9} e^{11} \right) - \frac{1}{2} P \right)

17

}

18

19 }

```

Listing 1. Implementation of the mEVP iteration Eq. (3). Stress and strain tensor components  $S^{11}, S^{12}, S^{22}, E^{11}, E^{12}, E^{22} \in \mathbb{R}^{N \times n_S}$  are stored as matrices where N is the number of elements and  $n_S$  the number of local DOFs in the stress space. Ice height and concentration are denoted as  $H, A \in \mathbb{R}^{N \times n_A}$ , where  $n_A$  is the number of local DOFs in the advection space. By  $H_{i,*} \in \mathbb{R}^{n_A}$  (and similar for the stress and the strain) we denote the local row vector of the DOFs belonging to element i. The matrices  $\mathrm{PSI}\langle n_A \rangle \in \mathbb{R}^{n_A \times n_G}$  are given at compile time and they evaluate the dG functions in the Gauss points with  $n_G$  being the number of Gauss points. The scalars  $P^*, \Delta_{\min} \in \mathbb{R}$  are physical parameters and constant for a simulation. The matrices  $M_i^{-1} \in \mathbb{R}^{n_S \times n_G}$  are pre-assembled and stored for each element. They represent the local inverse mass matrix scaled with the weights coming from the transformation of the mesh elements and multiplied with the matrix  $\mathrm{PSI}\langle n_S \rangle \in \mathbb{R}^{n_S \times n_G}$ . By "\*" we denote the element-wise Hadamard product of matrices.

|            | serial [s] | OpenMP (20 threads) [s] | speedup |

|------------|------------|-------------------------|---------|

| advection  | 188.32     | 34.34                   | 5.48    |

| boundary   | 38.30      | 11.25                   | 3.40    |

| strain     | 918.84     | 185.28                  | 4.96    |

| stress     | 1741.43    | 206.36                  | 8.44    |

| divergence | 1023.07    | 170.81                  | 5.99    |

| velocity   | 728.80     | 85.73                   | 8.50    |

| other      | 14.42      | 5.98                    | 2.41    |

| total      | 4653.2     | 699.75                  | 6.65    |

**Table 1.** Runtime of 120 time-steps of the simulation with  $2.6 \times 10^5$  elements on a 10 core CPU an Intel i9-10900X (10 cores @ 3.7 GHz). Except for the advection, all major computations are part of the mEVP iteration which performs 100 sub-steps in each time-step. Remaining operations, e.g. i/o and external forcing, are summarized by "other". For OpenMP, simultaneous multithreading is beneficial, as running with 20 threads is 24% faster than 10.

# 3.1 CUDA

150

The standard for general purpose GPU programming is CUDA (NVIDIA, 2023a), a C++ platform developed by NVIDIA. The primary interface is a C based language and API developed by NVIDIA with extensive compiler support for C++. CUDA has a mature ecosystem and gives low level access to the GPU, which allows one to develop highly optimized code. However, CUDA is limited to NVIDIA hardware and the development effort to obtain code with a high utilization of the available compute resources can be considerable.

Since version 3.3, Eigen has limited support for CUDA and allows one to use fixed sized matrices in CUDA kernels. Through this, we can use the code from Listing 1 largely unchanged. Eigen's manually vectorized code paths need to be disabled to have the code run on the GPU, but we still benefit from Eigen's other features such as expression templates and optimizations when a size is known at compile time. For the use of CUDA with Eigen, we have to ensure that the required data is in GPU memory. For dynamic buffers like  $S^{11}$  in Listing 1, we allocate memory manually and copy it-data as needed before and after the kernel invocation. Inside the CUDA kernel, an Eigen: Map is constructed with

160 1 **auto**

$$B = \text{Map} < \text{Matrix} < T$$

, Dynamic,  $n > > (\text{bufDevice}, N, n)$ .

This provides the same interface as the original matrix. For compile time matrices such as PSI we use the GPU's *constant memory*. Advantages of constant memory are that no manual memory management is required, faster memory access that memory access is faster through a dedicated cache, and that further compiler optimizations are possible since the values are available at compile time. In the original C++ CPU code, the constant matrices are defined as static class members with explicit template specialization to enable selection of the proper matrix for the specified dG-degree at compile time. Since

| optimization                                | time [s]                                                                   | speedup                       |

|---------------------------------------------|----------------------------------------------------------------------------|-------------------------------|

| CUDA baseline                               | $0.366 \pm 0.004$                                                          | 1.0                           |

| CUDA shared memory                          | $0.371 - 0.370 \pm 0.002$                                                  | 0.99                          |

| CUDA column-major                           | $0.419 \cdot 0.419 \pm 0.002$                                              | 0.87                          |

| CUDA on-the-fly map                         | $\underbrace{\textbf{0.323-}0.321\pm0.002}_{\bullet\bullet\bullet\bullet}$ | <del>1.13</del> - <u>1.14</u> |

| AdaptiveCPP-SYCL-AdaptiveCPP baseline       | $0.466 + 0.466 \pm 0.002$                                                  | 1.0                           |

| AdaptiveCPP-SYCL-AdaptiveCPP shared memory  | $0.531$ - $0.532 \pm 0.001$                                                | 0.88                          |

| AdaptiveCPP-SYCL-AdaptiveCPP on-the-fly map | $0.375 - 0.372 \pm 0.002$                                                  | <del>1.24</del> - <u>1.25</u> |

| Kokkos baseline                             | $0.522 - 0.522 \pm 0.001$                                                  | 1.0                           |

| Kokkos shared memory                        | $0.551$ $0.551 \pm 0.002$                                                  | 0.95                          |

| Kokkos on-the-fly map                       | $0.386 + 0.386 \pm 0.002$                                                  | 1.35                          |

**Table 2.** Total time spend on the stress computation for  $2.6 \times 10^5$  elements over 30 time-steps for the different implementations on an A100 GPU. Each modification is tested independently and speedup is relative to the respective baseline.

static member variables are not supported in CUDA, we instead declare separate variables and utilize **if** constexpr to achieve the same flexibility:

```

1 __constant__ constexpr T PSI_1_1[1] = {1.0};

2 template < int n, int n<sub>G</sub> > __device__ auto PSI(){

170 3 if constexpr (n == 1 && n<sub>G</sub> == 1) {

return Map < const Matrix < T, 1, 1 >> (PSI_1_1);

}

6 }

```

180

Another important modification for the use of Eigen on the GPU is the use of 32-bit integers as index type, since the default 64-bit integers are only emulated on the GPU.

We tried a number of optimizations to speed up the Eigen CUDA code, the results of which are shown in Table 2. The bottleneck on the GPU is often memory access. One remedy is the manual use of the L1-cache, called *shared memory* in CUDA. Shared between all threads in a thread block, it can significantly speed up reads of data that is needed multiple times and by multiple threads or when scattered memory reads/writes are necessary. In Listing 1, the only data that are used multiple times and by multiple threads are the PSI matrices. Only minor changes to the code are needed to load the PSI matrices into shared memory before use. However, we see no benefit from this change, cf. Table 2, since constant cache is just as fast for the compile time matrices. Shared memory would therefore only be worthwhile if we expect to run out of constant memory. However, the size of the compile time matrices depends only on the local degrees of freedom of the discretization. If we consider all of the implemented discretization orders together, roughly 26 KB of memory are needed. This is still less than half of the 64 KB constant memory available (NVIDIA, 2023a).

Another potential avenue to accelerate memory accesses is to carefully prepare the layout of the data. For the C++ CPU code, variables such as  $S^{11}$  are stored in row-major order, meaning that coefficients belonging to the same cell are contiguous in memory. This locality is beneficial both for effective cache usage and for vectorized memory accesses. On the GPU, the most efficient way to access global memory is through *coalesced* reads whereby neighboring threads access neighboring addresses. Since each thread processes one cell, this can be achieved by storing variables in column-major order. Nonetheless, as we can see in Table 2, the switch to column-major storage order leads to a measurable slowdown. A profiler revealed that the use of a column-major layout does improve the memory access patterns and the number of excessive sectors loaded from global memory decrease from 59~% for the row-major version to just 2~%. However, this difference is rendered ineffective by the cache. In particular, data that is seemingly loaded without need in the row-major version due to the strided access is, in fact, required by subsequent computations when it can be read from the cache. Furthermore, the column-major version performs more instructions for index computations, leading to the overall slowdown.

A third option to reduce global memory accesses is to trade off reads with more computations. This is beneficial when the code is memory-bound, as is often the case on the GPU, especially with classical linear algebra (Dublish et al., 2017). In our code, the I/O can be reduced by re-computing the inverse parametric map  $M^{-1}$ , which depends only on the geometry of the mesh and compile time constants. In particular, each matrix has a size of  $n_S \times n_G$  while each mesh cell's geometry is fully described by 4 vertices with 2 values each, which are furthermore shared with neighboring cells. So, disregarding constants, even for a small dG-degree such as  $n_S = 3$ , fewer reads are required if we compute the matrices on-the-fly, see also Richter et al. (2023a, Sect. 5.3.3). Upon closer inspection, we also find that when stored in column-major order, vertex reads are coalesced while reads to  $M^{-1}$  are not, due to the fact that  $M^{-1}$  is implemented as an array of matrices. Since the Eigen matrix type only deals with two dimensions, adjusting the storage order of  $M^{-1}$  to allow for coalesced accesses would be difficult. We find that the on-the-fly map computation computation of  $M^{-1}$  indeed delivers a speedup of 14 % over the CUDA baseline on an NVIDIA A100 GPU.

200

205

The above optimizations illustrate that GPU performance remains hard to predict and that for low level GPU programming, proper profiling is essential to identify bottlenecks and to develop efficient code. This applies not only to optimizations that address well-known bottlenecks, as above, but also to work on inconspicuous details in the code such as the order of expressions. An illustrative example of this is, again, found in the treatment of precomputed  $M^{-1}$ ; this is relevant in particular for higher order discretizations that will be examined in greater detail in Sect. 4.3. Accessing the matrix by reference or by making an explicit copy has no impact on the performance for smaller matrix sizes like  $3 \times 4$ . However, when  $M^{-1}$  has size  $8 \times 9$ , i.e. in a second order discretization, the copy results in a kernel that is 43% faster overall. Curiously, the slowdown with the access by reference is largely not caused by a memory bandwidth bottleneck. Instead, the massive number of unique memory accesses overwhelms the instruction queue that is responsible for executing cached memory accesses. The copy of  $M^{-1}$  alleviates this by encouraging the use of more registers to store the coefficients, thereby avoiding memory accesses.

## 3.2 OpenACC and OpenMP

220

225

230

235

240

245

A simple approach for moving computations to the GPU is to use a directive based programming model like OpenACC or OpenMP. In this case, only small or no changes to the code are required. Targeting C, C++ and Fortran, both OpenACC or OpenMP define directives to annotate loops. These instruct the compiler to offload the computations onto the GPU.

OpenACC or OpenMP differ in how the parallel execution is described. OpenMP is *prescriptive*, meaning that the programmer has to detail how a loop should be parallelized. On the other hand, OpenACC provides a simpler *descriptive* directive that leaves more decisions to the compiler. See (Usha et al., 2020) for more details on the differences between both approaches. In practice, OpenACC tends to give better performance (Usha et al., 2020; Đukić and Mišić, 2023). However, it has more limited compiler support. Except for basic support in GCC, OpenACC can only be used with experimental and commercial compilers that primary target NVIDIA hardware. Therefore, efforts exist to automatically translate OpenACC to OpenMP to access the larger ecosystem of OpenMP (Denny et al., 2018; Servat et al., 2022).

To accelerate our code, we tried three different compilers: GCC-12.2 and NVIDIA HPC-23.5 with support for both OpenMP and OpenACC, and Clang-16.0 which currently only supports OpenMP. However, we found that all three compilers fail for our code. The NVIDIA compiler refused to compile Eigen code, while GCC and Clang either crashed during compilation or produced a broken program that would crash once executed. Runtime crashes can be attributed to incorrect memory transfers, for which only Clang provided some diagnostics in the form of compile-time warnings. In particular, objects which are not trivially copy-able, such as Eigen matrices with at least one dynamic dimension, are not captured properly. While directives are provided to manually specify the needed buffers, this is cumbersome to do for the complicated template-based Eigen types in our code. Furthermore, it voids the main advantage of the directive based approach, namely its simplicity. Use of OpenMP and OpenACC was therefore not pursued further.

## 3.3 SYCL

SYCL (The Khronos Group, 2023a) is an open standard for heterogeneous computing developed by the Khronos group. The standard proposes a high-level API extending C++17 that allows the same code to run on various devices such as CPUs, GPUs and FPGAs. There are currently two major implementations of the SYCL standard, both of which are open source and build on LLVM. Development of AdaptiveCPP (Alpay and Heuveline, 2023), previously known as hipSYCL and OpenSYCL, is lead by Heidelberg University. While various backends are available, the focus is on NVIDIA and AMD GPUs. The other major implementation of SYCL is Data Parallel C++ (DPC++), which developed by Intel. DPC++ primarily targets Intel CPUs, GPUs and FPGAs.

SYCL builds on top of standard C++ to minimize the effort of adapting existing code. However, the SYCL standard forbids recursion and function pointers in kernel code (The Khronos Group, 2023b), both of which are used in Eigen's expression templates. DPC++ does not allow one to compile the neXtSIM-DG code because of these limitations, although the function calls should be entirely inlined in the compiled code. AdaptiveCPP requires more effort for setup but the tool chain compiles Eigen. We therefore limit our investigations to AdaptiveCPP in the following.

SYCL automates device memory management and movement of data between host and device, but memory requirements of a kernel need to be declared explicitly. To this end, a *buffer* needs to be defined, pointing to already allocated memory on the host. Then, a *command group* is created which collects all information needed to run a task in parallel. Inside the command group, *accessors* allow us to explicitly describe which buffers need to be accessed and how, i.e. read or write. Once pushed into a *queue*, the SYCL runtime uses these memory requirements as well as optional dependencies on other command groups to select the best suited memory region to perform needed memory transfers and to schedule the execution. Inside the command group, we can declare a parallel for-loop and construct Eigen maps analogous to CUDA with pointers provided by the accessors.

We can investigate the same optimizations as with the CUDA code. While shared memory did not improve performance for native CUDA, it is still of interest to see how it affects the SYCL implementation, since memory management works differently there. To access *local memory* in SYCL, which is the name used for CUDA's shared memory, we have to declare a *local\_accessor* in the command buffer. In addition, local memory only makes sense in the context of thread blocks, so we need to use a more complicated for-loop which makes thread blocks explicit. Unfortunately, such a construct is known to perform far worse on the CPU than a simple loop and work on reducing this gap is an active area of research (Meyer et al., 2023). Therefore, if the code is to be efficient both on CPU and GPU, local memory should be introduced only in code paths specialized for the GPU. For the code snippet under study, this additional effort was not considered worthwhile. Returning to Table 2 we see using shared memory makes the kernel moderately slower. On the other hand, computing  $M^{-1}$  on-the-fly leads to a more substantial relative speedup over the AdaptiveCPP baseline than the same optimization in native CUDA.

## 3.4 Kokkos

255

265

275

280

Kokkos (Trott et al., 2022) is another programming model to enable heterogeneous computing in modern C++, currently with support for CPU as well as NVIDIA and AMD GPUs. Kokkos is developed as part of the Exascale Computing Project by the US Department of Energy. The main difference to SYCL is that Kokkos is a library while SYCL requires compiler integration. The library-based approach greatly simplifies deployment of projects using Kokkos but potentially limits available possible optimizations and features.

Kokkos consists of macros and wrappers that provide a unified API for the different backends with the final code being processed by the chosen compiler. Therefore, we can once again start from the CPU code shown in Listing 1, knowing that it works in native CUDA. The primary mechanism to manage memory in Kokkos are *Views*, which are basically a shared pointer to a multi-dimensional array. Typically, both a device view and a mirrored host view are created to facilitate data transfers. For our use case, it is possible to create a view on already allocated memory with the *unmanaged* trait. However, unmanaged views do not play well together with the mirrored views concept in backend agnostic code, leading to unnecessary copies during the execution on the CPU. Since in general the device view needs its own buffer, copies between the mirrored views will be performed regardless of whether they already reside in the same memory space. These extra copies can be avoided by adding a special case for just the view creation on CPU and the CPU. They are therefore not a major problem for portability. Once

properly setup, data is accessible in the kernel through the device view and we can use the underlying pointer to create an Eigen map in the same manner as in CUDA.

Possible code optimizations in Kokkos are similar to those available in SYCL. CUDA's shared memory, called *scratch memory* in Kokkos, can be accessed by specifying a *TeamPolicy* with a thread block size instead of using a simple parallel for-loop. Here a nuisance of the library becomes apparent as the total scratch memory needed for a particular kernel has to be set manually. Furthermore, parallelism described with explicit thread blocks has the same downside as in SYCL, namely that it leads to strongly degraded CPU performance. In our tests we find that usage of scratch memory introduces a small overhead in Kokkos, see Table 2. On-the-fly map computation is again beneficial and it results in a large speedup of 35 %.

# 3.5 PyTorch

285

290

295

300

305

310

315

PyTorch (Paszke et al., 2019) is one of the most popular libraries for machine learning (Aoun et al., 2022). It consists of a simple-to-use Python frontend and a high-performance C++ backend that has a dedicated compiler to optimize code execution and maps execution for different hardware such as CPUs, GPUs, and TPUs. Full support is available for CPUs, NVIDIA GPUs and AMD GPUs.

To make effective use of PyTorch and the optimizations it implements, computations have to be reformulated in terms of large tensors. For this, we remove the main loop in Line 4 of Listing 1 and treat the element dimension N as the batch dimension of variable size. The matrix-vector products then become matrix-matrix products and element-wise operations remain unchanged. Some care is necessary to perform the products with the per-element inverse maps, e.g. Line 16. Since we have a third dimension in  $M^{-1}$ , this is not a standard matrix-matrix product. However, we can map this operation to a batched matrix-matrix product (bmm) by appending a dimension of size 1 to the second argument and removing it again afterward (squeezing in PyTorch terminology). Alternatively, we can formulate this computation as an element-wise product by adding a dimension corresponding to  $n_S$  to the second argument, followed by a sum over that dimension. The latter operation turns out to be 4 to 5 times faster across different backends, indicating that PyTorch is not tuned for our use case where the matrices are much smaller than those is common in machine learning workloads.

To integrate the PyTorch code into our C++ simulation, we have multiple options. With minor syntactic changes compared to the Python version, we can implement the computations directly with PyTorch's C++ API. However, this is inefficient since each operation is executed as a separate kernel with no kernel-fusion taking place, resulting in many reads and writes of the same data. A second option is to define the computation as a PyTorch model in Python. This model can be exported as *Torch-Script* and loaded in C++. Part of the C++ runtime is a just-in-time compiler which attempts to optimize the model execution on repeated use. However, more recent efforts to accelerate PyTorch models have been focused on *TorchDynamo*, a compiler first released with PyTorch 2.0. While the front-end of TorchDynamo is written in Python, various backends are available, some of which can be used without the Python runtime. Most promising among those we tested is the built-in *TorchInductor* which leverages the compiler Triton (Tillet et al., 2019) to produce highly optimized fused-matrix multiplications (PyTorch-devs, 2023). In particular, PyTorch 2.2 introduces AOTInductor, a version of TorchInductor that exports the entire model as a shared library with a single wrapper function to call directly from C++. Another way to deploy the PyTorch model in C++ is through

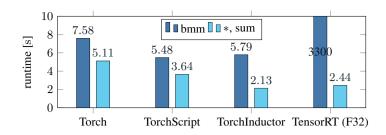

Figure 1. Total time spend on the stress computation over 30 time-steps for the different PyTorch variants on an A100. The products with  $M^{-1}$  are implemented either as batched matrix-matrix product (bmm) or element-wise product and sum (\*,sum). TensorRT uses single precision (F32) since double is not supported.

the extension Torch-TensorRT (Torch-TensorRT-devs, 2024), which uses NVIDIA's inference engine TensorRT (NVIDIA, 2023b) as backend. One limitation of TensorRT is that it does not support double precision.

We compare the four proposed variants to integrate the PyTorch model into C++ in Fig. 1. Although they use the same tensor primitives, the native C++ interface is considerably slower than TorchScript. The new compiler, TorchInductor, with its Triton-optimized kernels, is significantly faster than the alternatives when using the element-wise product. When implemented with bmm, the compiler fails to optimize the operation due to a lack of GPU memory. The fact that a batch size of  $2.6 \times 10^5$  is already too large, although the operands require less than 5 MB of memory, points to it being an edge case not properly considered by the optimizer. TensorRT is slower than TorchInductor for our use case, even while running in lower precision and has even more trouble with the bmm operation. Optimization of the model takes over a minute and the inference is orders of magnitude slower than the sum-based version.

# 3.6 Development and deployment effort

320

325

330

335

340

The development of dedicated CUDA code is time-consuming and error-prone. One purpose of the alternatives we considered in this work is to reduce this high development effort. Furthermore, most of them support a unified code for a variety of compute hardware. We therefore do a qualitative comparison of the different approaches, considering ease of development but also deployment of the finished code on a target system.

With their modern C++ interface, both Kokkos and SYCL make it easier to write correct code compared to CUDA. Simplified resource management and stricter types reduce the risk of memory related bugs and make more errors visible at compile time. The simple parallelism constructs also hide GPU specific scheduling based on blocks and grids from a developer. A further advantage of SYCL is that explicit annotations of device functions are unnecessary. SYCL's memory model fully automates transfers between host and device, eliminating another source of errors. It should be noted, however, that the more advanced C++ features used by Kokkos and SYCL can make the frameworks less approachable for non-C++ experts than the C-like interface of CUDA. PyTorch follows a completely different programming paradigm from the other options. While, when coming form From a system programming language backgroundperspective, PyTorch takes time to get used to, development

. Development in PyTorch is, however, overall much simpler. There is no memory management or explicit parallelism to take care of and rapid prototyping in Python is possible. A potential downside can be that some computations are hard to express in terms of tensor operations, in which case a low-level, manual implementation is still needed. Another downside for our particular case was that the code had to be completely rewritten in PyTorch, while for the other options the C++ CPU code could be largely reused.

For running the code on a target system, pure CUDA is easiest. Usually pre-installed on clusters, no additional setup is required. Furthermore, CUDA (or the AMD equivalent ROCm) is a prerequisite for the other frameworks to use the GPU, so if a manual installation is needed, this effort is unavoidable for every framework. The Kokkos library can be easily integrated into a project's CMake based build system and then works out-of-the-box. In combination with automatic fetching, e.g. via git submodule, the library setup becomes transparent. SYCL requires a specialized toolchain. For AdaptiveCPP, this means that its compiler wrapper has to be first build from source. The manual configuration that is needed for AdaptiveCPP to find the proper compilers is cumbersome and, in some cases, necessitate building a suitable version of LLVM first. For PyTorch, prebuild C++ libraries are available for all supported platforms. To use TorchInductor, the Python package is needed to generate the code on the target system, but it is easily acquired through a package manager.

## 4 Numerical experiments

345

350

355

360

370

To analyze the performance of our implementations, we use the established VP benchmark of a moving cyclone over a sea ice region (Mehlmann et al., 2021). We simulate a duration of 1 h, which requires 30 advection steps and 3,000 stress updates. For the discretization we choose first order continuous Galerkin (cG) elements and discontinuous Galerkin (dG) elements with 3 degrees of freedom for the advection. The original C++ CPU version of the code has already been validated on this benchmark, see (Richter et al., 2023a). We therefore compare to the CPU version to determine the accuracy of the computed results and note that, while there is no loss in accuracy between the implementations, deviations from double machine precision can cause visible differences in the results over longer time-scales. See Sect. 4.2 for additional details.

In the GPU implementations, significant time is required to transfer memory between host and device. Nonetheless, we only consider the kernel execution times in the following since the final objective of our work is a full GPU implementation of the dynamical core. While transfers are still necessary for coupling with other models, the major effort of simulating the sea-ice dynamics is in the mEVP iteration with the many sub-iterations considered in this work. This will amortize the costs of the memory transfers. Furthermore, they can potentially be hidden by overlapping them with computations. To ensure accurate timings, synchronization barriers are inserted as needed before and after the kernel invocation. In SYCL, memory transfers are implicit, so we rely on the built-in profiling instead to obtain the timings for SYCL-AdaptiveCPP. Details on the software and hardware used in the experiments are listed in Table 3.

|                       | System 1                                                  | System 2                           |  |

|-----------------------|-----------------------------------------------------------|------------------------------------|--|

| CPU                   | $2\times$ AMD EPYC Rome 7402, $2\times24$ cores @ 2.8 GHz | AMD EPYC 7A53, 64 cores @ 2.75 GHz |  |

| GPU                   | NVIDIA A100, 40 GB HBM2e                                  | AMD Instinct MI250X, 128GB HBM2e   |  |

| OpenMP (CPU) compiler | GCC-12.3                                                  | -                                  |  |

| GPU software stack    | CUDA 12.2                                                 | ROCm 5.6.1                         |  |

| Kokkos                | 4.1.0                                                     | 4.1.0                              |  |

| AdaptiveCPP           | 23.10.0 based on Clang-17.04                              | 23.10.0 based on AMD Clang-16.0    |  |

| PyTorch               | 2.3 Nightly (24-November-2023)                            | 2.2-2.4 (ROCm 6.1.2)               |  |

**Table 3.** The two systems on which performance measurements where conducted.

# 4.1 Performance scaling

380

385

390

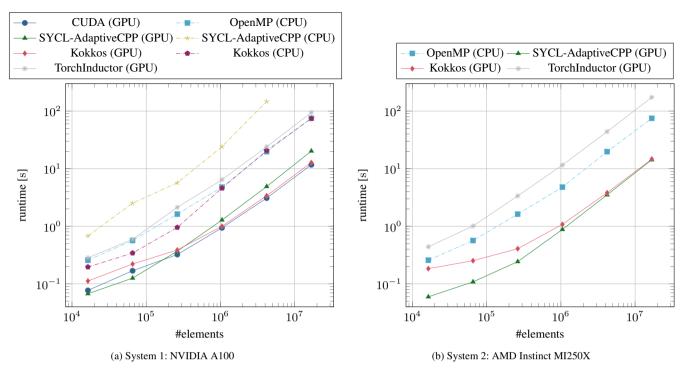

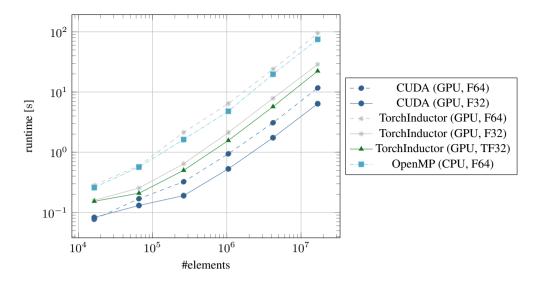

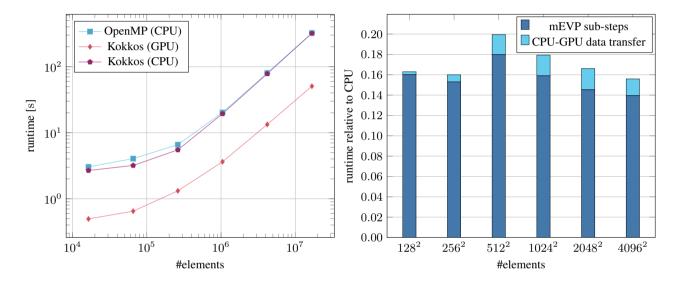

Of particular importance for coupled climate simulations is the scaling of the performance as a function of grid resolution. With a fixed domain size of 512 km, we reduce the cell size from 4 km to 0.25 km. This corresponds to an increase in the number of elements from  $1.6 \times 10^4$  to  $1.7 \times 10^7$  (i.e. one has a quadratic scaling of the element number in the resolution). In Fig. 2 we compare the best implementation for each approach as a function of elements for two different data center GPUs.

For the OpenMP reference we obtain the best results by utilizing all available threads with simultaneous multithreading enabled and the settings OMP\_PROC\_BIND=spread and OMP\_PLACES=threads. In the GPU versions of CUDA, Kokkos and AdaptiveCPPSYCL-AdaptiveCPP, we compute the inverse maps on-the-fly. In case of Kokkos and AdaptiveCPPSYCL-AdaptiveCPP, the simple for-loop is used to run the update in parallel, which also makes an execution on the CPU efficient, albeit with precomputed maps. For Kokkos on the CPU, we get the best results with the OpenMP backend and the same settings as raw OpenMP. For PyTorch, we take the implementation generated by TorchInductor with the element-wise product and sum.

Running on a NVIDIA A100 GPU (Fig. 2a), our CUDA implementation delivers a significant speedup over the OpenMP CPU reference implementation. For the smallest problem with  $1.6 \times 10^4$  elements, CUDA is 3 times faster, scaling up to 6.4 for  $1.7 \times 10^7$  elements. Kokkos achieves asymptotically the same performance as CUDA on the GPU and as OpenMP on the CPU. This is to be expected since the very same compilers (NVCC and GCC) are used by Kokkos and only memory buffers and kernel dispatch are abstracted. On small problems, Kokkos overhead makes it 50 % slower than CUDA but, surprisingly, the CPU version is slightly faster than raw OpenMP for the same number of elements. AdaptiveCPP-SYCL-AdaptiveCPP scales worse than the other GPU accelerated codes, being 70 % slower than CUDA for the largest problem size we tested. However, it still provides a significant improvement over the CPU OpenMP version running with 96 threads. The good performance of AdaptiveCPP-SYCL-AdaptiveCPP for small problem sizes is likely an artifact from the different time measuring method, since the SYCL timings do not fully account for the kernel launch overhead. However, since this cost does not scale with the number of elements, it becomes insignificant for larger problems where the GPU implementations are most useful. On the CPU, we were not able to run a meaningful experiment with AdaptiveCPPSYCL-AdaptiveCPP. Best performance was

**Figure 2.** Timings of the stress update using the best performing version for each framework. The size of the mesh cells size is scaled from 4 km to 0.25 km while keeping the domain size constant to increase the number of elements. On the AMD Instinct MI250X, only one of the two graphics compute dies (GCDs) is used. The values for OpenMP (CPU) are the same in both plots and where measured on System 4.1 with 96 threads.

achieved with a restriction to just 24 threads, indicating that the available CPUs are not utilized properly. The documentation states that performance of the CPU backend should be similar to raw OpenMP and that a significant deviation is likely caused by an improperly configured toolchain. However, we were unable to obtain stable results on three different systems, illustrating the substantially greater difficulty in using the framework compared to Kokkos. TorchInductor on GPU is slower than the OpenMP CPU code for every problem size tested and TorchInductor's CPU code (not shown) is an order of magnitude slower than the GPU version.

To test the portability of the heterogeneous compute frameworks we also ran the experiments on System 2, equipped with an AMD MI250X GPU. The results are shown in Fig. 2b. Kokkos, AdaptiveCPP—SYCL-AdaptiveCPP and PyTorch work without modifications but only utilize half of the MI250X, since it is a dual graphics compute die (GCD) design. AdaptiveCPP SYCL-AdaptiveCPP performs better on the AMD GPU, while Kokkos is somewhat slower than on the NVIDIA A100. Both thereby achieve a similar runtime, roughly 25 % higher than that of CUDA running on the A100. For PyTorch, the MI250X is 50 % slower than the A100 in our experiments. On paper, a single graphics compute die of the MI250X has the same memory bandwidth as the A100 and a F64 peak performance more than twice as high (A100 9.7 TFLOPS, MI250X 23.9 TFLOPS).

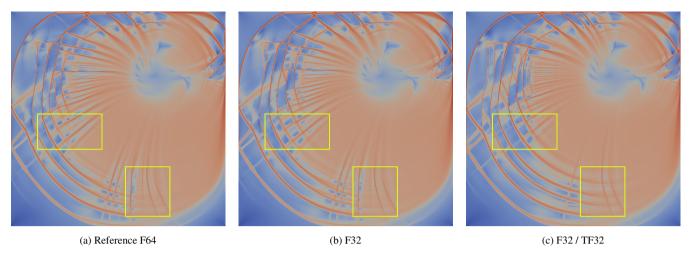

Figure 3. Shear deformation ( $\log_{10}$ ) for the benchmark after 48 h where the stress update is computed with different floating point types.

These results indicate that the AMD ecosystem is still less mature. However, with the performance currently achieved it is still a worthwhile target platform.

#### 410 4.2 Mixed Precision

420

425

One avenue to further speed up the simulation is to perform computations with lower precision float types. Switching from double precision (F64) to single precision (F32) halves the memory required and doubles the theoretical peak performance achievable on the a A100 (F64 9.7 TFLOPS, F32 19.5 TFLOPS). Modern GPUs support even lower precision types that promise further speed-ups. Of particular interest is tensor float (TF32), a format used in tensor cores, which are specialized matrix multiplication hardware found on NVIDIA GPUs and originally introduced for machine learning workloads. TF32 uses the same exponent as F32, so that the range of representable numbers is the same as for F32, combined with a half precision mantissa with just 10 bits that yields a significantly higher peak performance for matrix multiplications (156 TFLOPS) compared to F32.

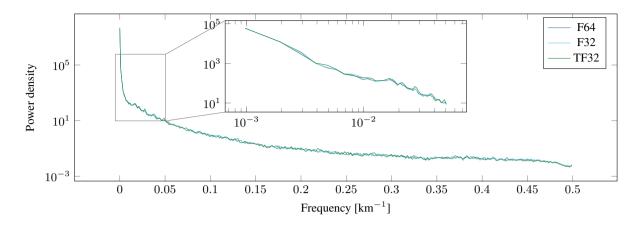

First we evaluate the impact of lower precision floats on the quality of the results. To this end, we perform the stress update in F32 while the rest of the simulation still runs in F64. To make use of the tensor cores, we run the PyTorch version, where TF32 can be enabled with a simple switch. Results for the benchmark after 48 h simulation time are shown in Fig. 3. Visually, F64 and F32 are indistinguishable, while some movement of larger cracks and additional fine features can be seen with TF32. Nevertheless, the overall distribution of features in the shear deformation remains very similar and there is good agreement in the frequency spectrum of the features, as can be seen in Fig. 4.

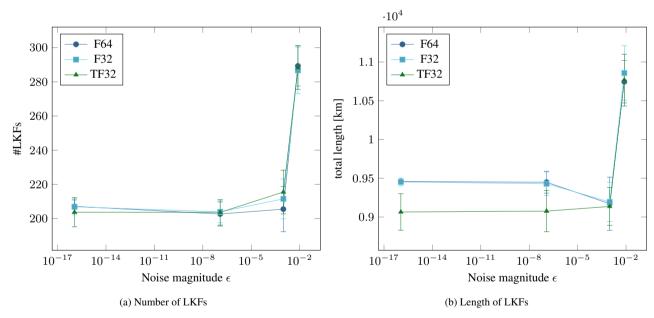

To quantify the stability of the physical model itself and whether computations with lower accuracy amplify instabilities, we look at the distribution of linear kinematic features (LKFs) (Kwok, 2001) using a script provided by Hutter (Hutter et al., 2019). We Hutter et al. (2019). In Fig. 5, we investigate the influence of randomly perturbed initial conditions on the formation of

**Figure 4.** Radially averaged power spectral density (RAPSD) of the shear deformation ( $log_{10}$ ).

Figure 5. Distribution of linear kinematic features (LKFs) after 48 h when the initial state of ice height H and ice concentration A are perpetuated with perturbed by adding uniform noise sampled from  $[-\epsilon, \epsilon)[-\epsilon, \epsilon)$  to each component of the fields. The noise Points show the mean of 24 randomized runs with a specific maximum magnitude is  $\epsilon$ , while the whiskers indicate the standard deviation. The  $\epsilon$  values are chosen as the interval machine precision for different floating point types, i.e.  $2^{-53}$  (F64),  $2^{-23}$  (F32),  $2^{-10}$  (F16/TF32),  $2^{-7}$  (BF16). Points show the mean of 24 runs, while the whiskers indicate the standard deviation.

**Figure 6.** Timings of the stress update for lower precision floating point types on the NVIDIA A100. The dashed lines are references in F64, taken from Fig. 2.

LKFs in the benchmark simulation. For F64 and F32, both mean and standard deviation are largely the same and perturbations up to F32 machine precision around  $10^{-7}$  appear to have no impact on the distribution. This indicates that, at least for short term simulations, F32 can be used without impacting the results. For TF32, there is a statistically significant deviation in the length of LKFs even for very small perturbations. However, the uncertainty in the sea-ice tracers from data assimilation is at least of the order  $10^{-2}$  or larger (Liu et al., 2019; Xie et al., 2017). In our experiment, the variation of the initial conditions has a larger effect on the LKFs than the floating point type used at this point, so TF32 could still be useful in practice.

430

435

The performance gains from switching the stress update to F32 or TF32 are plotted shown in Fig. 6. For CUDA, switching from F64 to F32 gives a speedup of 80 %, which is in line with the expected speedup for the A100. We, since both compute and memory throughput are effectively doubled. For this reason, we expect to see similar gains from using F32 in Kokkos and AdaptiveCPPSYCL-AdaptiveCPP, albeit with the different compiler of the latter, other factors including occupancy and the use of special function units could play a larger role. For TorchInductor, the relative speedup with F32 over the F64 version is much higher at 315 %. As machine learning tasks rarely use double precision, the optimizer is likely tuned much more for the single precision case. The variant with tensor cores enabled, TorchInductor (TF32), has a speedup of 412 % over F64 which is not quite as large as the theoretical peak performance would suggest. This is because not all operations can make use of the tensor cores and where it is possible, the matrices involved are too small to take full advantage of the tensor cores. In absolute terms, TorchInductor (TF32) still takes almost twice as long as CUDA (F64), even with access to tensor cores.

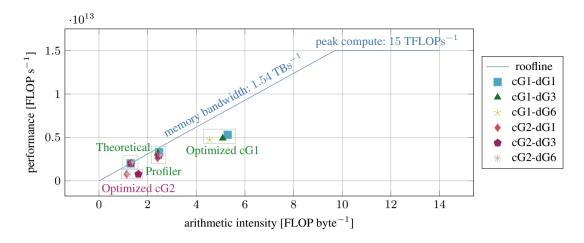

**Figure 7.** Roofline model of the F32 performance of the A100 with different variants of our CUDA kernel. Theoretical values are computed manually, while the other values are taken from Nsight Compute, the NVIDIA GPU profiler. The peak compute value given here assumes base clock speed to be consistent with the profiler results. Optimized kernels perform the on-the-fly map computation which is not viable for higher cG order.

# 4.3 Higher order scaling

455

460

Our finite-element code makes it easily possible to change the local number of degrees of freedom. So far we have focused on just one discretization, cG1-dG3, i.e. first order continuous Galerkin (cG) elements for velocity and 3 degrees of freedom discontinuous Galerkin (dG) for the advection. A higher order discretization significantly increases the compute loadwhich could make it. This could make the computations more efficient on the GPU when compared to the CPU, since the GPU is limited by memory bandwidth in our code. On the A100, compute throughput reported by the profiler for cG1-dG3 varies from 28 % to 50 %, depending on whether the precomputed maps are used, while the memory throughput is at 70 % to 80 %.

eG\dG  $n_A = 1$   $n_A = 3$   $n_A = 6$  1 ( $n_S = 3$ ,  $n_G = 4$ )1.30 1.31 1.31 2 ( $n_S = 8$ ,  $n_G = 9$ )1.29 1.32 1.38 Estimated arithmetic intensity of kernels with different discretization orders for F32. The roofline for the A100 is (or with boost clock). A simple roofline model of the A100 GPU is shown in Fig. 7. For our code, the relevant bottleneck is clearly the *arithmetic intensity*, i.e. the ratio of compute operations per byte accessed in global memory. The values reported by the profiler for our baseline kernels with precomputed maps are all close to the bandwidth limit, which underscores our observations from Sect. 3, i.e. that the only effective optimization is a reduction of the needed data data transfer per computation.

In contrast, the optimized kernels with on-the-fly parametric map computation present a different picture where neither memory bandwidth nor compute are a bottleneck. Instead, other limitations become apparent which can be attributed to the complexity of our kernel. One aspect that is exacerbated by the on-the-fly map computation, is the high number of registers that are needed by each thread. More temporary variables are needed and thoughalthough, for the tested cG1 kernels, these variables still fit in the registers, the higher register usage leads to a lower *occupancy*, i.e. the ratio of active warps that fit on each execution unit at the same time and the theoretical maximum supported by the hardware (for cG1-dG3: 57 % unoptimized,

| <u>cG∖dG</u>          | $n_A = 1$ | $n_A = 3$   | $n_A = 6$   |

|-----------------------|-----------|-------------|-------------|

| $1(n_S = 3, n_G = 4)$ | 1.30      | 1.31        | 1.31        |

| $2(n_S = 8, n_G = 9)$ | 1.29      | <u>1.32</u> | <u>1.38</u> |

**Table 4.** Estimated arithmetic intensity [FLOP byte<sup>-1</sup>] of kernels with different discretization orders for F32. The roofline for the A100 is  $9.73 \text{ FLOP byte}^{-1}$  (or  $12.5 \text{ FLOP byte}^{-1}$  with boost clock). The arithmetic intensity depends on the chosen degrees of freedom  $n_A$  in the dG advection space, as well as number of stress components  $n_S$  and gauss points  $n_G$  which are both determined by the cG order.

40 % optimized). As a result, the scheduler is unable to keep the different pipelines busy and more cycles are wasted just waiting.

While the gains in arithmetic intensity from the optimization are clearly worth it for cG1, cf. Table 2, the same is not true for cG2. With second order cG elements, the increased workload per thread, caused by the on-the-fly map computation, becomes a major problembottleneck. The computation involves a matrix inverse that becomes both too expensive and memory intensive for higher orders. For first order cG, this matrix has size  $3 \times 3$  and we can use a closed-form formula to compute the inverse that results in efficient code. For second order cG elements, the matrix has size  $8 \times 8$  and have to we we have to rely on a generic inverse implementation that becomes a major bottleneckalgorithm for matrix inversion. As we can see in Fig. 7, the arithmetic intensity of the "optimized" cG2 kernels is, in fact, lower than that of the kernels with precomputed maps because of a large number of temporary variables that end up getting are stored in global memory, since the available perthread register space is exhausted (in technical terms data is *spilled* to *local memory*). Subsequently, the unoptimized kernel is roughly 8 times faster. In the following, we therefore limit our analysis to the version with precomputed maps. Despite the lower arithmetic intensity, a higher order discretisation is still clearly more powerful when it comes to resolving the ice dynamics, see e.g. Mehlmann et al. (2021); Richter et al. (2023b).

To analyze the possible throughput independent of (sub-optimal) code generation, we also compute a theoretical bound based on the algorithmic description in Listing 1. For memory accesses we only count the data that is unique for each kernel invocation, i.e.  $S_{i,*}, E_{i,*}, H_{i,*}, A_{i,*}$  and  $M_i^{-1}$ , giving us a total of  $9n_S + 2n_A + n_S n_G$  float read and writes. For compute operations we only count float operations and assume F32, since in that case, all operations needed are native are native GPU instructions with well documented throughput (NVIDIA, 2023a). Additions are not counted since they can all be executed as fused-multiply-add, min and max have the same throughput as compute operations, and exp2 and sqrt<sup>-1</sup> count as 4 operations each (compute capability 8.0). Therefore, the total number of operations is

$$6n_S + 3n_A + 6n_S n_G + 2n_A n_G + 28n_G$$

465

giving us the theoretical arithmetic intensities recorded in Table 4. We can see that, in agreement with the profiler results, an increase in either order is insignificant for the arithmetic intensity. The largest difference of just 6 % is from cG2-dG1 to cG2-dG6, which should not have much of an impact on the memory access bottleneck.

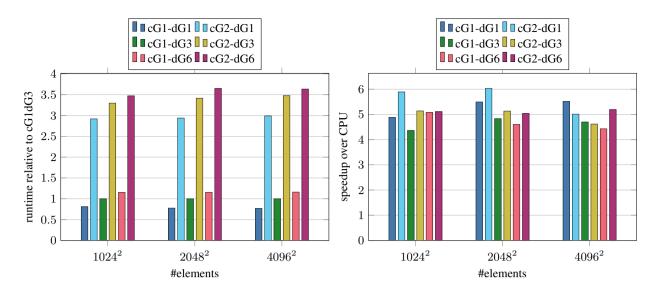

Figure 8. Performance of the CUDA implementation with precomputed map  $M^{-1}$  for different discretization orders on the A100. The three largest problem sizes from the scaling test are shown.

To verify this scaling model we measure the runtime for different discretization orders and compare with the OpenMP CPU baseline in Fig. 8. We find that the speedup from using the GPU ranges from 4.4 to 6.0 with no clear trend for either order parameter, inline with the theoretical prediction. The observed differences can mainly be attributed to the problem size impacting the behavior of the CPU version, since the relative runtime between the different GPU variants is very consistent across problem sizes.

## 5 NeXtSIM-DG implementation

495

500

Based on the results from Sect. 4 we <u>decide decided</u> on Kokkos for the full implementation of the neXtSIM-DG sea ice dynamical core. In our evaluation Kokkos <u>offers offered</u> performance almost competitive to CUDA but with greater ease of development, multi-vendor GPU support and the potential to replace the dedicated CPU implementation as well.

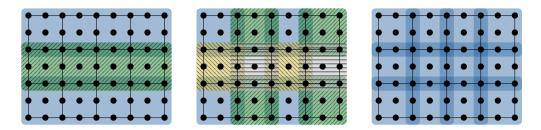

The port of the complete mEVP iteration to Kokkos is, for the most part, straightforward with the experience gained from the stress implementation implementation of the stress. Of note is the need for a different parallelization strategy for operations that involve neighboring cells of the mesh such as the divergence computation. In the OpenMP implementation, race-conditions are circumvented by performing the update in two steps, whereby every other row is processed in parallel (Richter et al., 2023a). However, as illustrated in Fig. 9, this parallelization strategy along just one dimension does not provide nearly enough work to saturate a GPU. One way to further increase parallelism without introducing contention at the edges is to perform four separate steps in a strided checkerboard pattern instead. Another way, that turns out to be faster for the divergence computation, is to

Figure 9. Parallel processing of biquadratic cG2-vectors. The mesh has 12 elements with  $N_x = 4$ ,  $N_y = 3$ . Each block corresponds to one thread and blocks of the same color can be processed in parallel. The maximum number of parallel tasks is, from left to right:  $\frac{N_y}{2}$  (row-wise),  $\frac{N_x N_y}{4}$  (strided),  $N_x N_y$  (atomic).

**Figure 10.** Timings of the full mEVP iteration on the NVIDIA A100 (System 1). The values for Kokkos (GPU) include the necessary data transfers between CPU and GPU. The CPU runs are with 96 threads.

process every cell in parallel and to rely on atomic operations to ensure that the values are updated correctly. The use of atomics in such a way could be suboptimal when running on CPU, but it does not appear to be a problem in our experiments.

505

Another concern for portability, also related to cross-cell updates, is the choice of the parallel loop construct. To easily address neighbors it can be tempting to use Kokkos's 2D range policy. However, this policy splits work into tiles instead of rows, which does not play well with our underlying data layout on the CPU. The whole mEVP update becomes 3 times slower on the CPU when using 2D-loops for strain and divergence computations, instead of 1D-loops with manual index computation. GPU performance is, in our case, largely unaffected by this choice.

| order   | base memory [MB] | per-element [KB] | max elements with 40 GB |

|---------|------------------|------------------|-------------------------|

| cG1-dG3 | 463.5            | 0.70             | $5.6\times10^{7}$       |

| cG2-dG6 | 463.5            | 3.44             | $1.2 \times 10^7$       |

**Table 5.** GPU memory usage for different discretization orders. A constant amount of memory is reserved by the runtime. Memory requirements for data scale linearly with the number of mesh elements, giving us an upper limit for the problem size on a 40 GB GPU like the A100.

## 5.1 Benchmark

515

530

535

While the new Kokkos code is not fully optimized yet and limited to F64, it already provides a sizable substantial speedup over the OpenMP code. Results for the benchmark setup described in Sect. 4 are presented in Fig. 10. In contrast to the previous experiments, the timings for the full mEVP iteration include the necessary data transfers to and from the device. Running on GPU, the mEVP iteration is faster by a factor of 6, even for small problem sizes. Running on CPU, the Kokkos code performs just as well as the OpenMP code. The cost of data transfers for the GPU version is still non-negligible at a constant 10 % for larger meshes, even though the 100 mEVP sub-steps are performed entirely on the device. This underlines the importance of minimizing necessary data transfers and running larger parts of a simulation fully on the GPUto minimize necessary data transfers.

Another important aspect of the GPU implementation are the device memory requirements. Especially due to the precomputed matrices, the available device memory does impose a practical limit on the mesh size. The memory requirements are recorded in Table 5. Apart from a constant part that is mostly reserved for the runtime and which varies slightly between devices, the memory usage scales linearly with the number of elements. A GPU with 40 GB VRAM can therefore fit roughly  $5.6 \times 10^7$  elements of order cG1-dG3. A switch to the higher order cG2-dG6 reduces the maximum number of elements to a little over one-fifth of that number.

As more parts of the simulation, such as the advection, are performed on the GPU, the memory requirements increase further. Possible strategies to reduce the device memory usage include moving buffers to RAM while they are not needed and to precompute only parts of the required maps to facilitate greater reuse between kernels. Both strategies are a trade-off between speed and memory. An alternative option is be to distribute the work across multiple devices. While this introduces synchronization overhead, the device memory usage itself should then not be a bottleneck as our results in Fig. 10 show that a single GPU can be well utilized with  $10^6$  elements or more.

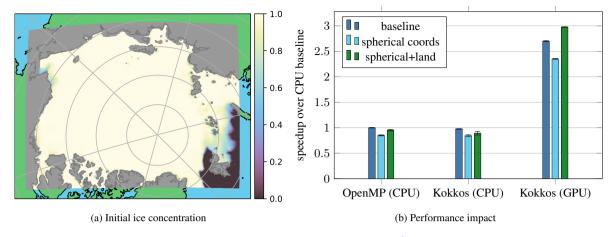

# 5.2 Realistic case

So far we have worked with an idealized test case in Cartesian coordinates that has a square domain which is completely covered by sea-ice except for a single boundary layer. In a realistic setting there will areas of land and open sea which do not need to be simulated. Although the parametric mesh can be deformed to closely fit a coast-line, the regular structure of the

Figure 11. A more realistic test case with a mesh of dimensions  $1240 \times 980$  ( $1.2 \times 10^6$  elements) and resolution 3.125 km covering the arctic. The data is for the 01 January 2010 with initial conditions and ocean forcing derived from TOPAZ4 reanalysis (Sakov et al., 2012) and ERA5 reanalysis (Hersbach et al., 2020) for atmospheric forcing. Performance measurements are taken on a system with  $2 \times$  AMD EPYC 7773X (64 cores each), using 122 OpenMP threads in total and a NVIDIA H100 PCIe. Factors that affect the performance compared to the benchmark test case are the use of spherical coordinates and a land mask (gray) which leaves only 68 % of the cells active. Performance values shown are relative to the idealized CPU (OpenMP) baseline without land and with Cartesian coordinates. Whiskers indicate the standard deviation from 8 runs.

mesh will leave some computational cells inactive when more complicated geometry is involved. We therefore considered also a more realistic setup in our experiment, see Fig. 11. Once again, the OpenMP reference and Kokkos (CPU) versions perform very similar. The GPU baseline is around 2.7 times faster than the CPU. The smaller performance gap compared to previous experiments can be explained by the differences in hardware. The CPUs are significantly faster and we use 122 physical cores instead of 48 as before. While the H100 that is used for the experiments is also faster than the A100 in the other experiments, the main bottleneck, the memory bandwidth, does not improve significantly form the A100 (1.6 TB) to the H100 PCIe 2 TB.

540

545

550

Spherical coordinates, which introduce additional scaling terms, lead to a performance penalty of around 15 % for all tested variants. The land mask, which deactivates updates for one-third of the domain, has little impact on the CPU. With a 12 % improvement for OpenMP and 6 % for Kokkos (CPU), the final measured times are slightly slower than the baseline. The small improvement from the land mask is because of the static parallel schedule, whereby each thread receives the same number of elements to update, leaving the thread with the most active elements to determine the overall speed. This will be addressed in the MPI version of the code, where the domain decomposition can take into account land cells. The GPU version, on the other hand, can already take advantage of the inactive cells to some extent, since work is split into many small warps, which finish instantly when they consist entirely of land. In fact, a speedup of 26 % from setting the land mask makes the GPU code faster overall for the realistic case than for the idealized baseline. To get this speedup, there needs to be larger areas of land and

the mesh resolution has to be sufficiently high, so that the ratio of warps consisting of both active and inactive cells is small compared to the total.

The different characteristics regarding the land mask lead to the first platform specific adoption in our code. For kernels like the stress, which do not affect neighboring cells, land checks are optional and consequently inserted in the GPU version, but left out when compiling for the CPU. The presented values in Fig. 11 already include this optimization.

Finally, the memory usage does not change for the realistic case, so the values in Table 5 remain valid. The additional values used for spherical coordinates are currently loaded on to the device regardless of whether they are needed. The land mask has no effect since the space for land cells in the field arrays still has to be allocated to allow for direct access of the cell-data with computed indices.

## 6 Conclusions

555

560

565

575

580

We implemented and evaluated different options for the GPU parallelization of the neXtSIM-DG dynamical core. According to our results, CUDA remains the most reliable option both in terms of performance and with regard to the toolchain. Thanks to the CUDA support of Eigen, we were also able to use the CPU C++ code with minimal modifications in CUDA.

Kokkos benefits in the same way from Eigen's CUDA library support, while SYCL does not need explicit support which makes it well suited for an incremental port of existing C++ code in general. The streamlined memory model and simplified parallel constructs of Kokkos and SYCL facilitate more effective development, but at some performance cost. Using dedicated GPU features such as shared memory remains an issue because it leads to code that is very inefficient on the CPU, breaking the promise of the heterogeneous computing paradigm. However, our study demonstrates that this specialization is not always needed to achieve good performance and we can therefore recommend Kokkos as an alternative to CUDA. While SYCL shares the same benefits on paper, it suffers from immature implementations and is currently too unreliable for practical use.

PyTorch currently lacks far behind the more conventional options in terms of performance and is therefore mostly worth considering for rapid prototyping. However, the optimizer heuristics are clearly far from optimal yet for our use case and the underlying compilers are developing quickly, so we expect performance improvements in the future. Furthermore, PyTorch and similar machine learning frameworks are interesting alternatives because of their ease of development and the access to automatic differentiation they provide. The latter is of great relevance for hybrid methods that combine a conventional discretization with a machine learning component, e.g. Bedrunka et al. (2021); Kochkov et al. (2021); Demeure et al. (2023); Kochkov et al. (2023).